# $C\lambda$ asH: From Haskell To Hardware

Master's Thesis

of

Christiaan Baaij

Committee: Dr. Ir. Jan Kuper Ir. Marco Gerards Ir. Bert Molenkamp Dr. Ir. Sabih Gerez

Computer Architecture for Embedded Systems Faculty of EEMCS University of Twente

December 14, 2009

# **ABSTRACT**

Functional hardware description languages are a class of hardware description languages that emphasize on the ability to express higher level structural properties, such a parameterization and regularity. Due to such features as higher-order functions and polymorphism, parameterization in functional hardware description languages is more natural than the parameterization support found in the more traditional hardware description languages, like VHDL and Verilog. We develop a new functional hardware description language,  $C\lambda$ asH, that borrows both the syntax and semantics from the general-purpose functional programming language Haskell.

In many existing functional hardware description languages, a circuit designer has to use language primitives that are encoded as data-types and combinators within Haskell. In  $C\lambda$ asH on the other hand, circuit designers build their circuits using regular Haskell syntax. Where many existing languages encode state using a so-called *delay* element within the body of a function,  $C\lambda$ asH specifications explicitly encode state in the *type*-signature of a function thereby avoiding the node-sharing problem most other functional hardware description languages face.

To cope with the direct physical restrictions of hardware, the familiar dynamically sized lists found in Haskell are replaced with fixed-size vectors. Being in essence a subset of Haskell,  $C\lambda$ asH inherits the strong typing system of Haskell.  $C\lambda$ asH exploits this typing system to specify the dependently-typed fixed-size vectors, be it that the dependent types are 'fake'. As the designers of Haskell never set out to create a dependently typed language, the fixed-size vector specification suffers slightly from limits imposed by the typing system. Still, the developed fixed-size vector library presents a myriad of functionality to an eventual circuit designer. Besides having support for fixed-size vectors,  $C\lambda$ asH also incorporates two integer type primitives.

$C\lambda$ asH can be used to develop more than just trivial designs, exemplified by the reduction circuit designed with it. The  $C\lambda$ asH design of this reduction circuit runs only 50% slower than a hand-coded optimized VHDL design, even though this first generation  $C\lambda$ asH compiler does not have any optimizations whatsoever. With the used FPGA resources being in the same order as the resources used by the hand-coded VHDL we are confident that this first-generation compiler is indeed well behaved.

Much has been accomplished with this first attempt at developing a new functional hardware description language, as it already allows us to build more than just trivial designs. There are however many possibilities for future work, the most pressing being able to support recursive functions.

# Acknowledgements

At the end of my *Informatica* bachelor I was convinced (as naïve as I was, and probably still am) that enjoyable intellectual challenges could only be found in the intersection of the fields of Electrical Engineering and Computer Science. That is, most Computer Science courses, given a few exception, in my curriculum were simply not that challenging, and hence, not fun. The exceptions were, perhaps unsurprisingly in retrospect, Functional Programming and Compiler Construction.

As I started my master's degree on Embedded Systems, I never thought that those two subjects would play such an important role in my master's thesis. When I was in the office of professor Smit, looking for a subject for my thesis, I was told that Jan Kuper had some ideas for a project. Jan's description of the project literally was (be it that he said it in Dutch): "Do you remember those functional description I showed in ECA2? That's what I want. To make real hardware out of them". Quite a vague description, and not the type of project I was expecting to find, but very interesting nonetheless; a chance to go back to those subjects of Computer Science I found interesting during bachelor and combine it with my (limited) acquired knowledge of hardware designs. It only took a few moments of deliberation to come to the conclusion that this project would indeed be a joy to work on.

Only a month into the project I was joined by Matthijs, of whom I am certain that he could have written the entire compiler himself, had he not been so busy organizing all those large events of his. I am glad I was able to work with him on this project, as he is certainly an enjoyable person to both work, and hang around with. I think we are both happy with the final result, having even been able to go to the official Haskell conference in Edinburgh to present our work. For this success, I most certainly want to thank Jan, for both initiating this great project, and always giving me much welcomed guidance when I was unsure what to work on next.

I also want to thank Bert for always being there to answer questions about VHDL (when I was perhaps too lazy to look for an answer myself), and of course I also want to thank Marco for helping me understand the design of his reduction circuit, and for aiding me in my work in general.

Last, but certainly not least, I would like to thank my mother, for her never ending love, and having always supported me during my studies.

# Table of Contents

| Lis | et of Acronyms                                                                                                                                                        | vii                     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1   | Introduction       1.1 Our new functional HDL: $C\lambda$ asH        1.2 Assignment        1.3 Overview                                                               | 1<br>1<br>4<br>5        |

| 2   | Domain2.1 Properties of Hardware Description Languages2.2 Existing Functional HDLs2.3 Signals and State2.4 Generating Netlists: Problems & Solutions                  | 7<br>7<br>9<br>11<br>12 |

| 3   | Hardware Types  3.1 Dependent Types  3.2 Fixed-Size Vectors  3.3 Integers                                                                                             | 15<br>15<br>18<br>32    |

| 4   | Case Study: Reduction circuit 4.1 The input buffer                                                                                                                    | 39<br>41<br>43          |

| 5   | Discussion       5.1 Combining higher-order functions with fixed translations        5.2 Separation of Logic and State        5.3 Haskell is Lazy, Hardware is Strict | 45<br>45<br>46<br>48    |

| 6   | Conclusions 6.1 Future Work                                                                                                                                           | <b>51</b> 52            |

| A   | Vector Function Templates                                                                                                                                             | 59                      |

| В   | Test bench Generation                                                                                                                                                 | 71                      |

| C   | Solutions for the Node Sharing Problem                                                                                                                                | 73                      |

| D   | Haskell Constructs & Extensions                                                                                                                                       | 77                      |

| E   | CλasH Generated VHDL                                                                                                                                                  | 83                      |

| Bil | bliography                                                                                                                                                            | 89                      |

# LIST OF ACRONYMS

ADT Algebraic Data Type

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

AST Abstract Syntax Tree

CAES Computer Architecture for Embedded Systems

**C**λ**asH** CAES Language for Hardware

**CPS** Continuation-Passing Style

DSL Domain Specific Language

EDIF Electronics Design Interchange Format

EDSL Embedded DSL

FD Functional Dependencies

FIFO First In, First Out

FIR Finite Impulse Response

FPGA Field-Programmable Gate Array

GADT Generalized ADT

GALS Globally Asynchronous, Locally Synchronous

GHC Glasgow Haskell Compiler

HDL Hardware Description Language

IP Intellectual Property

MoC Model of Computation

MPTC Multi-Parameter Type Classes

PCB Printed Circuit Board

RAM Random-Access Memory

$SM \times V$  Sparse Matrix Vector multiplication

VHDL VHSIC HDL

VHSIC Very High Speed Integrated Circuit

CHAPTER

# Introduction

A Hardware Description Language (HDL) is any language from a class of computer languages and/or programming languages for formal descriptions of digital logic and electronic circuits. The most famous HDLs are VHSIC HDL (VHDL) [20] and Verilog [19]. These languages are very good a describing detailed hardware properties such as timing behavior, but are generally cumbersome in expressing higher level properties such as parameterization and abstraction. For example, polymorphism was only introduced in the 2008 standard of VHDL [20] and is unsupported by most, if not all, available VHDL simulation and synthesis tools at the time of this writing.

A class of HDLs that does prioritize abstraction and parameterization, are the so-called functional HDLs. Through such features as higher-order functions, polymorphism, partial application, etc. parameterization feels very natural for a developer, and as such, a developer will tend to make a highly parameterized design sooner in a functional HDL than he would in a more 'traditional' HDL such as VHDL. The ability to abstract away common patterns also allows functional descriptions to be more concise than the more traditional HDLs.

Another feature of (most) functional HDLs is that they have a denotational semantics, meaning that we can actually *proof* (with the help of an automated theorem prover) the equivalence of two designs. Though not further explored in this thesis, such equivalence proofs, could be used to *proof* that an highly optimized design has the same external behavior as the simple behavioral design the optimized design was derived from, eliminating the need for the exhaustive testing usually involved in the verification of optimized designs.

Even though the development of functional HDLs started earlier than the now well known HDLs such as VHDL and Verilog, these functional HDLs never achieved the same type of fame: at the time, the ability to make a highly parameterized designs in a natural way, and the ability to abstract common patterns, were not as important as the details you can specify with VHDL or Verilog. However, with the increasing complexity of todays hardware designs, and the amount of effort put into exhaustively testing these designs, the industry might soon recognize the merits of functional HDLs.

# 1.1 Our new functional HDL: $C\lambda$ asH

The CAES group came with the idea of investigating the use of functional hardware description as both a research platform for hardware design methodologies, but also as an educational tool

2 Introduction

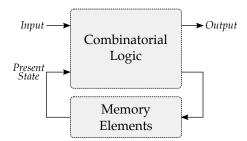

Figure 1.1: Basic Mealy Machine

to be used in practical assignments on hardware designs. The basic premise was that all hardware designs describe the combinatorial logic of a Mealy machine [30]. A graphical representation of a Mealy machine is shown in Figure 1.1. A Mealy machine is a finite state machine that generates an output, and updates its state, based on the current state and the input. We can simulate such a Mealy machine in a functional language, using the straightforward *run* function shown in Code Snippet 1.1. This simulation function basically maps the input over the combinatorial logic using the state as an accumulator.

CODE SNIPPET 1.1 (Simulation of a Mealy Machine).

```

run _ _ [] = []

run func state (input: inputs) = output: outputs

where

(output, state') = func input state

outputs = run func state' inputs

```

So the *func* argument represents the combinatorial logic of the Mealy machine, and the *state* argument of course represents the memory element. So, the actual hardware we will have to describe is the function *func*, whose most basic design can be seen in Code Snippet 1.2.

CODE SNIPPET 1.2 (Mealy Machine Logic).

```

func :: InputSignals → State a → (OutputSignals, State a)

func input state = (output, state')

where

...

```

The state of the hardware design is modeled as just a regular argument of the function, and is as such made very explicit. Many existing functional HDLs hide the state within the body of the function; so in this aspect, the functional descriptions we propose really stands out from the rest.

When compared to a more traditional HDL such as VHDL, we can see how the abstraction of state in the proposed functional descriptions allows for a clear synchronous design. In Figure 1.2 we can see the description of a Multiply-Accumulate circuit in both a functional HDL and in the more familiar VHDL. Only by looking at the type of the functional description, it is already clear which part of the design will be part of the state of the circuit. However, if we examine the VHDL description, it is only due to our a-priori knowledge that the *clk* signal will not always have a rising edge, that we can infer that the circuit will have to 'remember' the value of the *acc* signal.

#### I.I.I THE SOURCE

Now that the basic idea behind our new functional hardware descriptions is there, we have to think about what kind of syntax, semantics, etc. we want. In this, we have several options: We can

```

entity macc is port (clk, resn: in

std_logic;

macc ::

(Integer, Integer) \rightarrow

integer

x, y

: in

: buffer integer );

State Integer \rightarrow

(Integer, State Integer)

end entity macc;

macc(x, y) acc = (u, u)

architecture RTL of macc is

where

signal acc: integer;

u = acc + x * y

begin

u \Leftarrow acc + x * y

runMacc = run \ macc \ 0

acc \Leftarrow 0 when resn = '0' else

u when rising_edge (clk);

end architecture RTL;

```

Figure 1.2: Multiply-Accumulate: Functional HDL vs VHDL

either define the syntax and semantics ourselves, and write a parser for this language etc. We can also embed it as a Domain Specific Language (DSL) inside another language, where we encode the hardware in custom data-structures. Or, we can use an existing language as a source language and write our functional descriptions in this language.

The first option requires us to write our own parser, type-checker, etc. If we choose the second option we have to write a special interpretation function so that we may simulate the hardware description, and another function to translate it to hardware. For the third option, leveraging an existing language, we can take all the existing tooling (if available) and modify it so that we can translate the Abstract Syntax Tree (AST) of the compiled source to hardware.

Writing our own parser, type-checker, etc. seems too much of an effort when we are still in the exploration phase of our functional hardware designs, so for now, the first option will not be explored any further. The second option, embedding a DSL in an existing language is certainly appealing. We get all the parsing and type-checking for free, as it is provided by the host language, and we get to define our own syntax and semantics. This route has been taken by many other existing languages, some of which are shown in Chapter 2.

The third option, leveraging an existing language, gives us many of the same benefits as the an Embedded DSL (EDSL). The existing syntax and semantics are a double-edged sword of course: all the syntax and semantics is already defined, so we get all that for free. However, some of the existing language elements might have no meaning in hardware, so we have to teach a user of our language not to use those language elements. At the start of this master's assignment we did not yet fully appreciate/understand the merits of embedding a DSL in a host language, so the decision was made to leverage an existing functional language for our hardware descriptions. This has certainly not been a poor choice as we have successfully implemented many aspects of a functional hardware description language. Not only that, with this option explored, we can now also investigate how leveraging an existing functional language compares with the EDSL approach to designing functional HDLs.

There are many functional programming languages to use as the basis for our functional HDL: LISP [40], Haskell [34], ML [31], Erlang [3], etc. Of all these possible possible languages to leverage, we chose Haskell [34]. Even though we did not compare all the options to see which would suit functional hardware specifications the most, Haskell certainly has many features that make it a good choice. It has a strong type system that helps a designer to specify certain aspects of the hardware design upfront, before implementing the body of the function. It was developed to be *the* standard for functional languages. Also for us, as designers of a new functional HDL, there are many benefits: There is a whole set of existing open-source tools and compilers, including the

Introduction

highly optimized flagship Haskell compiler: the Glasgow Haskell Compiler (GHC).

#### I.I.2 THE TARGET

We do not only want to use our new language to specify and simulate hardware, we also want to generate the actual hardware from our descriptions. Solutions such as programming a Field-Programmable Gate Array (FPGA) directly are not really a sane exercise, so we have to translate our descriptions to a format that allows other tools to do this for us. The most basic (textual) hardware description that every FPGA programming software understands, is a netlist: A format that describes how the basic electronic components and gates are connected to each other. The most common netlist format is Electronics Design Interchange Format (EDIF); actually, its specification covers all aspects of electronic design: schematics, netlists, mask layout, PCB layout etc. The EDIF format is however too low-level for our current needs, which is just being able to synthesize functional specifications so that they can run on a FPGA<sup>1</sup>.

As a netlist is too low-level, we will use an existing higher-level HDL that already has available tooling to translate to a netlist format as the target language of our compiler. At the start of this thesis, the higher-level HDL that met this requirement, and that we were most familiar with, was VHDL. VHDL can be synthesized to a netlist format as long as we restrict ourselves to a certain subset of the language. Having VHDL as our target language also gives us the advantage of having access to the optimizations in the existing VHDL synthesis tools. Maybe having an even higher-level HDL (such as BlueSpec [4]) as our target language, would have saved us some translations steps when turning Haskell into this target language. However, it would have taken us considerable time to familiarize ourselves with such a language and the corresponding tools.

As such, the initial goal for the project is set: to design the tools for our new language, which is a subset of Haskell, so that we may simulate our functional hardware descriptions and also translate them to synthesizable VHDL. We call this new language:

CAES Language for Hardware ( $C\lambda$ asH)

# 1.2 Assignment

The original goal of the project soon proved to be too large for one master's assignment, so the work was divided over two assignments. The thesis of Kooijman [26] describes the general translation from Haskell programs to VHDL descriptions. The focus of Kooijman [26] lies on reducing higher-order, polymorphic functions to first-order, monomorphic function and then translating these normalized functions to VHDL. The focus of the work described in this thesis lies on the type aspects of  $C\lambda$ asH and the simulation of the hardware descriptions. Also, where the work of Kooijman [26] describes the general translation to VHDL, the work in this thesis describes specific translations concerning certain types, data-structures and the functions on these data-structures.

The reason that this thesis so specifically focuses on types and simulation, is that, even though Haskell has established itself as a successful functional programming language, it still remains to be determined if its properties are equally useful for functional hardware descriptions. A highly regarded property of Haskell is its strong typing system, and this thesis will mostly focus on how we can use this type system to specify the types in our hardware descriptions. Besides being able to translate our descriptions to actual hardware, we of course also want to simulate our descriptions (in Haskell).

<sup>&</sup>lt;sup>1</sup>As optimization is not a goal of our current language and tooling, it seems wise not to target Application-Specific Integrated Circuits (ASICs) for the time being.

1.3. Overview 5

# 1.3 Overview

This thesis continues in Chapter 2 with discussing existing functional HDLs, naming their merits, problems and solutions. Then Chapter 3 holds the bulk of this thesis, describing the design and implementation of the hardware specific types for our language  $C\lambda$ asH. To show what is possible with this first incarnation of  $C\lambda$ asH we examine a small case study in Chapter 4. As this is the first version of  $C\lambda$ asH we ran into a few problems during its design, we discuss a few of these problems in Chapter 5, ultimately making our conclusions in Chapter 6. Many master's assignments are never complete, always finding new opportunities to improve the original work; this thesis is certainly no exception, so we describe possibilities for future work in Section 6.1.

As supporting material for this thesis, there are also a few appendices. Appendix A shows the VHDL translations for all the functions of our new Haskell vector library. We then have Appendix B, which goes into the details of our automated VHDL test bench generation, which was developed to verify the correctness of the generated VHDL. Appendix C discusses some solution for the node sharing problem encountered in many existing functional HDLs. Appendix D gives a short introduction to some of the GHC extensions to Haskell, that are relevant to this thesis. It is meant for a reader with some experience with functional languages, but not with Haskell and the GHC extensions to Haskell. Readers unfamiliar with Haskell are stressed to read this appendix before continuing with the rest of this thesis. The last appendix, Appendix E, finishes with a  $C\lambda$ asH description of a 4-tap FIR Filter, and the corresponding, generated, VHDL code. It is included in this thesis to give the reader an idea of what the generated VHDL looks like.

#### I.3.I TYPESETTING

This thesis involves a lot of code snippets, and also references to those code snippets. For this reason, we try to distinguish between types, function, etc. by trying to use different typesetting for each of these elements:

- Function *names* are printed *italic*.

- Type names are printed in a medium bold, sans font.

- Both function variables and type variables are printed italic.

- Code that is *inlined* in the text is typeset in the same way as the *code snippets*.

- Library NAMES are printed in SMALLCAPS.

# 2

# **DOMAIN**

Hardware Description Languages (HDLs) have been around for some time, the popular ones: VHDL and Verilog both emerged around the mid 80's. But some functional HDLs, like DAISY [21] and  $\mu$ FP [38] were actually developed earlier. This chapter tries to give a short overview of those earlier functional HDLs, and also of the more recent ones like Lava [8] and ForSyDe [35]. We will touch on their merits and faults, and explain the so-called *node sharing* problem that many languages encountered in their design; solutions to this problem are however reserved for Appendix C. This is done because  $C\lambda$ asH differs from many existing functional HDLs, and does not suffer from the *node sharing* problem. Most of the information in this chapter comes from an earlier assignment [5] on the exploration of existing functional HDLs.

# 2.1 Properties of Hardware Description Languages

The functional HDLs we will see in this chapter are all *structural* descriptions of *synchronous* hardware. Some languages, like  $C\lambda$ asH, do however allow some *behavioral* aspects in the hardware descriptions. This section tries to informally introduce the meaning of the earlier mentioned terms, like *structural* and *synchronous*.

#### 2.1.1 STRUCTURAL AND BEHAVIORAL DESCRIPTIONS

For a trivial circuit designs it might suffice draw a transistor layout, but a slight increase in complexity warrants the use of some kind of hierarchy in the design. In the general case a single hierarchy is not sufficient to properly describe the design process. There is a general consensus to distinguish *three* design domains, each with its own hierarchy. These domains are:

- The behavioral domain. In this domain, a part of the design (or the whole) is seen as a black

box; the relations between outputs and inputs are given without a reference to implementation of these relations. The highest behavioral descriptions are algorithms that may not even

refer to hardware that will realize the computation described.

- The structural domain. Here, a circuit is seen as the composition of sub-circuits. A description in this domain gives information on the sub-circuits used and the way they are interconnected. Each of the sub-circuits has a description in the behavioral domain or a

8 Domain

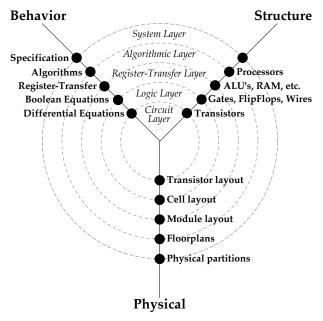

Figure 2.1: Gajski Y-Diagram

description in the structural domain itself (or both). A schematic showing how transistors should be interconnected to form a NAND gate is an example of a structural description, as is the schematic showing how this NAND gate can be combined with other logic gates to form some arithmetic circuit.

• The physical (or layout) domain. A circuit always has to be realized on a chip which is essentially two-dimensional. The physical domain gives information on how the subparts that can be seen in the structural domain, are located on the two-dimensional plane. Fore example, a cell that may represent the layout of a logic gate will consists of mask patterns that form the transistors of this gate and the interconnections within the gate.

The three domains and their hierarchies can be visualized on a so-called *Y-chart* [11] as depicted in Figure 2.1. Each axis represents a design domain and the level of abstraction decreases from the outside to the center. It was introduced by Gajski in 1983 and has been widely used since then.

Some of the design actions involved in circuit design can clearly be visualized as a transition in the Y-chart either within a single domain or from one domain to another. These are *synthesis* steps; they add detail to the current state of the design. Synthesis steps may be performed fully automatically by some synthesis tools or manually by the designer. Tools that translate designs that are in structural domain to designs in the physical domain are usually called *Place & Route* tools. Large circuit are usually designed in a HDL. These HDLs usually allow for both descriptions in the structural domain and the behavioral domain, sometimes allowing even annotations related to the layout (physical domain). Automated synthesis for the behavioral set of those languages is usually limited or sub-optimal, due to the complexity of the involved problems, such as automated scheduling, and the analysis of complex memory access patterns.

# Designs approaches in this thesis

The functional HDL we will see in this chapter all belong to the class of *structural* HDLs, in that they (only) support designs in the *structural* domain.  $C\lambda$ asH is currently also a *structural* HDL,

though it also has aspects that belong the *behavioral* design domain. For example, it has support for choice elements and integer arithmetic.

#### 2.1.2 SYNCHRONOUS AND ASYNCHRONOUS HARDWARE

The kind of hardware we will deal with in this report is *synchronous* hardware. In synchronous hardware, every component obeys the same omnipresent clock. The semantics of synchronous circuits are quite simple, and can be modeled as functions from input streams, and some state, to output streams. Some *synchronous* circuits have components that run at different, but related speeds, mostly through the use of a clock divider circuit. It is still a *synchronous* circuit as there is still a single clock that dictates all the other clocks. When modeling this kind of synchronous hardware, extra measures have to be taken to properly update the different memory elements.

A more general approach is *asynchronous* hardware, where different components listen to different, unrelated clocks (usually called Globally Asynchronous, Locally Synchronous (GALS)). Some *asynchronous* hardware design have no clock at all. Asynchronous hardware is usually very difficult to reason about, as such, it is hard to find a semantic model which is powerful enough to predict what is going on in the circuit at the electronic level, and simple enough to reason with from the point of view of a designer.

The functional HDLs described in this chapter, like  $C\lambda$ asH, can only model *synchronous* circuit where *all* components run at the same clock frequency.

#### 2.2 Existing Functional HDLs

There have been many functional hardware description languages over the years, usually made obsolete by their successor. This section starts with the two predecessors,  $\mu$ FP [38] and Ruby [22], of the still actively researched language: Lava. Lava, the third language we touch on, is one of the most extensively documented functional HDLs, and was the main focus of the individual assignment [5] leading up to this thesis. The fourth and final language is ForSyDe, of which part of its compiler (the VHDL AST) is even used in C $\lambda$ asH. Readers interested in other existing functional hardware description languages are referred to the individual assignment of Baaij [5].

#### 2.2.1 $\mu$ FP

$\mu$ FP [38] extends the functional language, FP [6], designed for describing and reasoning about regular circuits, with synchronous streams.  $\mu$ FP advocates descriptions using only built-in connection patterns, also called combinators. An example of such a combinator is a *row* combinator, which, when applied to a list of circuits, for each circuit in the list connects the output to the input of the consecutive circuit. The result of applying this combinator to this list of circuits, is a single larger circuit, which has only one input and one output.

A result of only being allowed to use these combinators is that one is not allowed to give names to intermediate values or wires, which might lead to awkward circuit descriptions. However, according to Claessen [8], a big advantage of this connection pattern style that  $\mu$ FP advocates, is the ease of algebraic reasoning about circuit descriptions: Every built-in connection pattern comes with a set of algebraic laws.

## 2.2.2 RUBY

The idea of connection patterns was taken further in the relational hardware description language Ruby, which can be seen as the successor of  $\mu$ FP. In Ruby, circuits and circuit specification are seen as relations on streams. Ruby also supports built-in connection patterns that have an interpretation

10 Domain

in terms of layout. Like  $\mu$ FP, Ruby descriptions might get awkward because one is forced to use the connection style pattern.

#### 2.2.3 LAVA

# Chalmers-Lava

Lava is a hardware description language embedded in the functional language Haskell. There are two versions of Lava in use. The one described in this section, Chalmers-Lava [8] is developed at Chalmers University of Technology in Sweden and is mainly aimed at interfacing to automatic formal hardware verification tools.

Lava facilitates the description of *connection patterns* so that they are easily reusable. Lava also provides many different ways of analyzing circuit descriptions. It can simulate circuits, just as with most standard HDLs, but can also use symbolic methods to generate input to analysis tools such as automatic theorem proves and model checkers. The same methods are used to generate VHDL from the Lava circuit description. To give a better understanding of how those symbolic methods work, an example of a symbolic Signal API is shown in Code Snippet 2.1.

CODE SNIPPET 2.1 (Symbolic Signals).

```

\begin{array}{ll} \textbf{data } \textit{Signal} = \textit{Var String} \mid \textit{Component (String, [Signal])} \\ \textit{invert } b &= \textit{Component ("invert" [b])} \\ \textit{flipflop } b &= \textit{Component ("flipflop" [b])} \\ \textit{and } a \ b &= \textit{Component ("and" [a, b])} \\ \dots \end{array}

```

So a signal is either a variable name (a wire), or the result of a component which has been supplied with its input signals. When we build a description out of the above primitive components we are actually building a data-structure that represents a signal graph. As we now have an actual graph, we can use standard graph traversal methods which makes the analysis methods for these descriptions a lot easier to design and implement.

# Xilinx-Lava

The Xilinx version of Lava [39] is almost similar to the Chalmers version but focusses more on the Xilinx FPGA products and has been used to develop filters and Bezier curve drawing circuits. It also has support for specifying the actual layout of the different components on the FPGA slices.

# 2.2.4 FORSYDE

ForSyDe [35] is implemented as an EDSL on top of the Haskell programming language. Its implementation relies on many Haskell extensions, some of which are exclusive to GHC, such as Template Haskell<sup>1</sup>. Two different sets of features are offered to the designer, depending on the signal API used to design the hardware:

# Deep-embedded

The deep-embedded signal Application Programming Interface (API), is based on the same concepts as the symbolic methods in Lava: By encoding the signals as data-structures, a traversal of a hardware description will expose the structure of the system. Based on that structural information, ForSyDe's embedded compiler can perform different types of analysis and transformations.

$<sup>^{1}\</sup>mathrm{More}$  information about Template Haskell can be found in Section D.5.

2.3. Signals and State

It has a back-end for translation to synthesizable VHDL, and also a back-end for simulation. Even though it would be possible to simulate the generated VHDL, instead of simulating the original circuit description, debugging a design using the simulation back-end is most likely faster than generating and simulating the VHDL for each debug iteration. The *deep embedded* signal API only supports synchronous descriptions (or synchronous Model of Computation (MoC), in the ForSyDe terminology).

#### Shallow-embedded

Shallow-embedded signals are modeled as streams of data isomorphic to lists. Systems built with them are unfortunately restricted to simulation (the traversal algorithms work only on symbolic signals), however, shallow-embedded signals provide a rapid-prototyping framework with which to experiment with different types of MoCs. The models of computation that are supported are the Synchronous MoC, the Untimed MoC, and the Continuous Time MoC. Also, ForSyDe has so-called Domain Interfaces which allow for connecting various subsystems, regardless of their MoC.

# 2.3 SIGNALS AND STATE

All (functional) hardware description languages have to deal with how to model the electronic signals that will eventually flow through the actual hardware. A complete physical model is often overly complicated, so usually an abstraction of a signal is used. In C $\lambda$ asH, a synchronous HDL, a signal is modeled to have a single steady value for a particular tick of the clock.

Many other functional HDLs are often more data-flow like, in that a signal is modeled as a stream (an infinite list) of values, one for each clock cycle. Instead of thinking of a signal as something that changes over time, it is a representation of the entire history of values on a wire. This approach is efficient for many functional HDL when simulating the hardware, because lazy evaluation and garbage collection combined keep only the necessary information in memory at any time. To give a better feel for this stream-based approach, we see an And-gate as it would be modeled in a stream-like language in Code Snippet 2.2

CODE SNIPPET 2.2 (AND-Gate in a stream-based approach).

```

\begin{array}{c} \textit{andGate} :: [\textit{Bool}] \rightarrow [\textit{Bool}] \rightarrow [\textit{Bool}] \\ \textit{andGate } \textit{a} \textit{ b} = \textit{zipWith} (\land) \textit{ a} \textit{ b} \end{array}

```

Simulating this And-gate for three clock cycles with signal *a* having the values [*True*, *True*, *False*] and signal *b* having the values [*False*, *True*, *True*], will give the expected output: [*False*, *True*, *False*]. Note that the above lists are finite only for the purposes of presentation.

Almost all functional descriptions of hardware require that each circuit acts like a pure mathematical function, yet real circuits often contain a state as well. To model this state in the stream-based approach we delay a stream by one or more clock cycles. Looking at the external behavior, it now seems as if the circuit description can recollect the state of the signal of one or more clock cycles ago. To give an idea of how this works, we show the description of one of the most primitive stateful components you typically find in hardware, a delay flip-flop, in Code Snippet 2.3<sup>2</sup>.

CODE SNIPPET 2.3 (Stream-based Delay flip-flop).

```

flipflop :: [Bool] \rightarrow [Bool]

flipflop \ a = False : a

```

<sup>&</sup>lt;sup>2</sup>In many papers on functional HDLs that use *streams* to model signals, this code example is often referred to as a *latch*, which is incorrect, as the stream definition clearly states that it represents signal values for entire clock cycles; latches can change value during a cycle.

12 Domain

This description hard-codes the initial state of this delay flip-flop to *False*, but we could of course make the description parameterized in this aspect.

# 2.4 Generating Netlists: Problems & Solutions

When a circuit contains a feedback loop, its corresponding graph will be cyclic. For example, take a trivial circuit with no inputs and one output, defined as follows:

CODE SNIPPET 2.4 (Oscillate circuit).

```

inv :: [Bool] \rightarrow [Bool]

inv \ a = map \ (\neg) \ a

oscillate :: [Bool]

oscillate = flipflop \ (inv \ oscillate)

```

Assuming that the flip flop is initialized to *False* when power is turned on, the circuit will oscillate between *False* and *True* forever.

Perhaps the deepest property of a pure functional language is referential transparency, which means that we can always replace either side of an equation by the other side. Now, in the equation:

$$oscillate = flipflop (inv oscillate)$$

(2.1)

We can replace the *oscillate* in the right hand side by any value  $\alpha$ , as long as the following holds:

$$\alpha = \textit{oscillate}$$

(2.2)

And we do: the entire right hand side is equal to *oscillate*. The same reasoning can now be repeated indefinitely:

```

oscillate = flipflop (inv oscillate)

= flipflop (inv (flipflop (inv oscillate)))

= flipflop (inv (flipflop (inv (flipflop (inv oscillate)))))

...

```

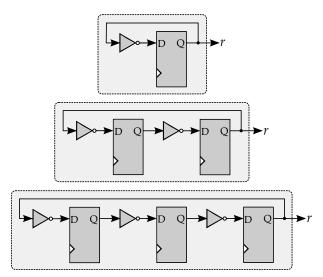

All of these circuits have exactly the same behavior. But it is less clear whether they have the same structure. Figure 2.2 shows the circuits corresponding to the above equations. So, depending on how many times you want to evaluate the description in Code Snippet 2.4, the corresponding structure might be any of the circuits in Figure 2.2; or even all three circuits in parallel, depending if hardware is generated for each iteration.

It is absolutely essential for a hardware description language to be able to generate netlists. We must find a way to determine if we already visited a node as we traverse the circuit graph, so that we can describe the desired feedback loop. The problem thus becomes that we need to be able to uniquely determine each node in the graph. The problem can be circumvented by only evaluating a function once, at the cost of losing the ability to evaluate recursive functions.

#### 2.4.1 Node sharing in $c\lambda$ ash

The problem of not knowing the exact structure of a circuit description with a feedback loop does not apply to  $C\lambda$ asH. That is because such a feedback is not made as explicit as they are in other existing functional HDLs, which are more data-flow like. Take the  $C\lambda$ asH description of the oscillation circuit for example:

```

oscillate :: State Bool \rightarrow (Bool, State Bool) oscillate (State s) = (s, State (\negs))

```

Figure 2.2: Several oscillation circuits

Compared to the general circuit description found in Code Snippet 1.2, we see that this circuit has no input signals. The **State** type indicates that the only input of the function is the state of the function, which is of type **Bool**. The function signature also indicates that the output of the function is of type **Bool**.

To get back to the issue of node sharing in  $C\lambda$ asH: The connecting element between the updated state and the present state is not visible on evaluation of the circuit description, so there can be no endless evaluation of a circuit description akin to what we witnessed in the earlier oscillation circuit description. There is no doubt that the  $C\lambda$ asH description precisely corresponds to the structure of the top instance of the oscillation circuits portrayed in Figure 2.2. We will only witness endless evaluation of this circuit if the we apply the circuit description to the *run* function found in Code Snippet 1.1.

What this means is that there is no need for  $C\lambda$ asH to uniquely determine nodes in the circuit graph to support feedback loops. Actually, the *only* type of feedback loops you can *explicitly* describe in a  $C\lambda$ asH function are purely *combinatorial* feedback loops. And since we do not want to make purely combinatorial loops in hardware, there is no reason for a  $C\lambda$ asH compiler to support descriptions that have those feedback loops. Many existing functional HDLs do suffer from the node sharing problem however, so compilers of these languages had to find ways to uniquely determine graph nodes. The interested reader is referred to Appendix C to see a number of approaches to uniquely determine these graph nodes.

# HARDWARE TYPES

As  $C\lambda$ asH is basically just a subset of Haskell which is translatable to VHDL,  $C\lambda$ asH gets all the benefits (and burdens) of Haskell's strong type system. Throughout this chapter we discuss whether the type specification needs for a HDL can be met by Haskell's type system. A very important property of types in HDLs is that they are able to specify the size of an object; something we also see in many of the VHDL types, such as **array** and **unsigned**. The reason why size is so important in hardware specifications is that without knowing this property there is no way we can determine the ultimate structure of the hardware. These size-dependent hardware types are part of a larger class of types called *dependent types*.

This chapter begins with an informal introduction of such dependent types in Section 3.1. As Haskell does not have real dependent types we will also see how they can be *faked*. The limits imposed by this *fakery* play an important role in the ultimate design of the fixed-size vector type, which we discus in Section 3.2. We add support for vectors in  $C\lambda$ asH as they are an ubiquitous concept to conveniently group elements. So the second section of this chapter discusses the design process behind the current implementation of fixed-size vectors in  $C\lambda$ asH, how they work under simulation, and how they are translated to VHDL. As we do not want  $C\lambda$ asH to be a purely structural language, we have added support for a very important behavioral concept: integers and their corresponding arithmetic operators. Section 3.3, which is the final section of this chapter, discusses the design of the integer primitives in  $C\lambda$ asH, how they function under simulation, and finally how they are translated to VHDL.

# 3.1 Dependent Types

Concepts, such as *programs*, *programming languages*, *computations* and *types*, are probably familiar to most readers of this thesis. So to make a potentially long story short: Programming languages are used to express computations. Computations manipulate values. Typed programming languages distinguish between *types* and *values*. Types are related to values by a *typing relation* that says what values *belong* to what types, so one usually thinks of *types* as a *set of values*. Expressions, and other program parts, can be *assigned* types, to indicate what kind of values to produce or manipulate. Types can thus be used to document programs (to clarify what kind of values are involved in a certain part of the program) and to help detect programmer mistakes.

In statically typed languages, the types are not seen as something that take part in computations, but rather something that allows a compiler to check that a program is *type correct* without actually running the program. Seeing types as a way to organize values, one can ask the question whether it would be meaningful to have a similar way to organize types? Or to even have values aiding in the organization of types? The answer is yes, and this is where dependent types come in.

Dependent types reflect the fact that validity of data is often a *relative* notion by allowing prior data to affect the types of subsequent data [29]. Types are first class objects in dependent types systems: they may be passed as arguments and computed by functions from other types or from ordinary data. Type-level programming is just ordinary programming which happens to involve types, and the systematic construction of types for generic operations is correspondingly straightforward, as we will see later on in this chapter. This thesis is not the place for a full explanation of dependent types, so a reader in search of (a lot) more detail is referred to works such as those by Barendregt [7] and Luo [27]. However, a more pragmatic approach to understanding dependent types might to experiment with them in a dependently typed language like Agda [32], which has a Haskell-like syntax. The standard example of a dependent type is the type of lists of a given length<sup>1</sup>:

```

data Vector :: Nat \rightarrow Type \rightarrow Type

where [] :: \forall (A :: Type). Vector Zero A

(:) :: \forall (A :: Type). \forall (n :: Nat). A \rightarrow Vector n A \rightarrow Vector (Suc n) A

```

The above states that a **Vector** type is constructed out of a natural number (**Nat**) and another arbitrary **Type**. The *datatype* has two constructors, the empty vector, [], which results in a **Vector** with length *Zero*. The second constructor, (:), concatenates an element to a vector of length n, resulting in a vector whose length is the **Successor** of n. The presence of explicit length information allows us to enforce stricter static control on the usage of vector operations. For example, we ensure that the *tail* operations is applied only to *nonempty* vectors:

```

vTail :: \forall (A :: Type). \forall (n :: Nat). Vector (Suc n) A \rightarrow Vector n A

vTail (x : xs) = xs

```

Programming with dependent types is much less convoluted in practice than it might seem at first glance because the compiler can fill in the details which are forced by the type, such as the **A** and *n* arguments for vTail. In addition, the need for 'exception handling' code is greatly reduced: vTail has no [] case, because [] is not in its domain.

# 3.1.1 DEPENDENT TYPES IN HASKELL

Haskell's developers did not set out to create a type-level programming facility, but non-standard extensions with *Multi-Parameter Type Classes* (MPTC) and *Functional Dependencies* (FD) (and more recently also *Type Families*) nonetheless provide the rudiments of one, albeit serendipitously. The concepts behind *Multi-Parameter Type Classes*, *Functional Dependencies* and *Type Families* are explained in greater details in Appendix D. These extensions to the Haskell *type class* mechanism give us strong tools to relativize types to other types. We may simulate some aspects of dependent typing by making *counterfeit* type-level copies of data, with type constructors simulating data constructors and type classes simulating datatypes.

Unless a reader is already quite familiar with the mentioned Haskell constructs, all of the above will probably sound quite alien. For this purpose we will give a short introduction to type-level programming in Haskell. We do this by first defining a 'familiar' term-level representation and afterwards showing the type-level equivalent. The example will consist of some very basic arithmetic relations, be it that we might use some unfamiliar encoding of natural numbers: Peano numerals.

$<sup>^{1}\</sup>mathrm{The}$  reader should note that the example is not Haskell code.

Peano numerals encode natural numbers using the two basic constructs which we saw earlier when we encoded the length property in the dependently typed vector type: The *Zero* construct represents the natural number 0, and the *Successor* construct (of course) represents the successor of a Peano encoded natural number.

To start, we will define these Peano encoded natural numbers (and an abbreviation for a sample number) in Haskell at the *term*-level:

```

data Nat = Zero | Succ Nat

three = Succ (Succ (Succ Zero))

```

The 'counterfeit' type-level copy of the above datatype could then be constructed as follows:

```

data Zero

data Succ n

type Three = Succ (Succ (Succ Zero))

```

So where *Zero* and *Succ* were constructors for the **Nat** type in the *term*-level example, they are now *types* in their own right. And the sample number is now also a *type* on its own right (be it that it is 'just' a type *alias*).

Now that we have these natural numbers we want to define a function that tells us if a number is even or odd, at the *term*-level we do that as follows:

```

even \ Zero = True

even \ (Succ \ n) = odd \ n

odd \ Zero = False

odd \ (Succ \ n) = even \ n

```

We will now define these *even* and *odd* functions at the type level using Haskell's type-class mechanism. Details of the type class mechanism can be found in Appendix D and will not be elaborated any further in this section. For now, the type class specific syntax should just be seen as the required syntactic sugar for type-level programming. The *type*-level functions are defined as follows:

```

class Even n where is Even :: n

instance Even Zero

instance Odd n \Rightarrow Even (Succ n)

class Odd n where is Odd :: n

instance Even n \Rightarrow Odd (Succ n)

```

The *isEven* and *isOdd* functions specified in their respective classes are defined as a matter of convenience, and could be discarded. We defined these functions so it is easier to ask a Haskell interpreter to check if a number is even (or odd). So using the class functions we can ask a Haskell interpreter to check if the earlier defined *type*-level number **Three** is even or odd:

```

GHCi> :type (isEven :: Three)

*** Error:

No instance for (Odd Zero)

arising from a use of 'isEven' at <interactive>:1:0-5

Possible fix: add an instance declaration for (Odd Zero)

```

We get a type error because three is not an even number. An interpretation of the last line is that if zero were odd, then three would be even.

```

GHCi> :type (isOdd :: Three) (isOdd :: Three) :: Three

```

The absence of a type error means that three is an odd number.

The given example certainly does not touch on all of the *type*-level programming facilities found in Haskell, nor the simulation issues of dependent types in Haskell; this thesis is not the place for such work. However, there is a lot of excellent material available on these subjects. A good introductory tutorial on type-level programming in Haskell is *Fun with Functional Dependencies* by Hallgren [14]. Readers who are keen on knowing more about the simulation of dependent types in Haskell in general will certainly enjoy reading Conor McBride's article: *Faking It: Simulating Dependent Types in Haskell* [29].

# 3.2 FIXED-SIZE VECTORS

In general-purpose programming languages, and also HDLs, lists/vectors are used to conveniently group elements, such as bits. In many programming languages we can deal with dynamically sized vectors (e.g. linked lists), or even infinitely large vectors when we apply a lazy evaluation strategy. In HDLs however, both concepts are problematic in their physical realization on hardware. As we do not have an infinite amount of resources, such as floor space, infinite lists that expand in space are out of the question. Infinite lists that expand in time are beyond the scope of this thesis, as  $C\lambda$ asH designs can only describe the structural properties of hardware.

To have dynamically sized lists, we would have to reconfigure the layout of the hardware at run-time. With ASICs this is impossible; and even though some FPGAs do allow for runtime reconfiguration, it is virtually impossible to use this feature for scaling purposes such as dynamically sized lists. The reason being of course that it is hard, or even impossible, to determine beforehand the upper bound of the required floor space for the dynamically sized list. Also, we would need to design dedicated hardware on the FPGA that will do all this runtime reconfiguration while the chip is running.

In the end this means that it is paramount for a HDL to support fixed/statically sized lists, from here on called fixed-size vectors. Recognizing this almost obvious need for fixed size vectors, and having Haskell's type system at our disposal, we would of course like to specify the size at the type level. There are two very important reason why we would like to specify the exact length of a fixed-size vector at the *type* level (information available at compile-time), and not at the *term* level (information usually only available at run-time):

- When the exact length of a vector is specified at the *type* level, it is statically available at compile-time. This makes the VHDL translation of the vector type and the operations on vectors very straightforward, as VHDL also needs the length of its arrays to be specified as part of their type. If the size of the vector where to be specified at the *term* level, the compiler will need to do a lot of partial evaluation and bookkeeping to know the exact length of the vector at any time in the compilation process. This becomes even harder when vectors can change length by a variable amount. Also, when we have a purely combinatorial circuit with a vector as one of its inputs there is the problem of the inability to specify the size of this input vector at the *term* level. We would have to take special matters, such as specifying a compiler pragma, to let the compiler know how big the input vector is.

- The type checker will help the engineer in designing correct hardware, as he can specify, in the signature of the function, what the length of the input vectors should be, and what the length of the output vectors will be. This way you do not have to do an exhaustive simulation to find conflicting vector sizes, as they will be caught at compile time.

In Haskell we can easily specify function signatures for functions that work on unconstrained vectors (implementation details omitted for purposes of presentation):

```

head :: Nat n \Rightarrow Vector \ n \ Int \rightarrow Int

head = ...

```

3.2. Fixed-Size Vectors

Where the type variable *n* indicates the length of the vector; note that by specifying the context *Nat n* we try to indicate that the variable *n* is some sort of natural number. Ideally we would then like to have something that allows us to specify a vector with a specific length along the lines of:

Where we say that v is of a **Vector** type containing 23 values of type Int. Alas, it is not possible to directly specify the above in Haskell: the *term*, 23, is not allowed on the right side of the double colon (::); only *types* may venture there. As we saw in the previous section however, we can *simulate* dependent types in Haskell by making a *type*-level copies of data/terms. So in a way, we can have something quite similar to the defined **Vector** type. We will just use a *type-level numeral*, akin to natural numbers from the previous section, to parameterize the vector.

Beside the need to specify the size of the vectors, we also want to specify transformations on the size of the vectors, or how the size of two vectors relate to each other. Because the size of the vectors is a type, the operations will of course also have to work directly on types. For example, we want to be able to specify that the size of a vector resulting from the concatenation of two vectors is the combined size of the two input vectors:

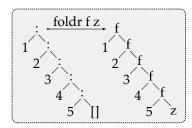

$$(++)$$

:: Vector s1  $a \rightarrow Vector$  s2  $a \rightarrow Vector$   $(s1 + s2)$   $a$

We start our investigation with an existing library that already has all of the above features. This fixed-size vector library, called FSVEC [1], has been developed as part of an existing functional HDL mentioned in Chapter 2: ForSyDe [35].

#### 3.2.1 FSVEC LIBRARY

The FSVEC library uses the type-level numerals from the TYPE-LEVEL library [2] to indicate the size of the vector at the type level. This type-level numerals library uses *Multi-Parameter Type Classes* and *Functional Dependencies*<sup>2</sup> to specify the relations between the numerals, and the operations on them, like the summation (+) operator in the type signature of the above (++) function. In this subsection we will deal with the particulars of the FSVEC library and the TYPE-LEVEL library at the same time as we explore the functionality of FSVEC. We start with the datatype that represents the fixed-size vector:

**newtype**

$$Nat s \Rightarrow FSVec s \ a = FSVec \{ unFSVec :: [a] \}$$

The **newtype** keyword indicates that the datatype definition is actually a datatype renaming from the list type, [a], to **FSVec s a**. In this sense it is not a 'true' datatype; the exact details of **newtype** declarations can be found in Appendix D. The context of the datatype, the part before the  $\Rightarrow$  symbol, means the following: *Nat s* implies that the type variable *s*, the size of the vector, is a numeral that belongs to the set of natural numbers. The natural number, *s*, is thus not a *term literal*, but a *type*. For example, the number two is represented by the *type* **D2**, where the **D** indicates that is is a decimal representation<sup>3</sup>. If you want to use these *type*-level numerals in the body of a function, you have to use some sort of *term*-level representations, as types are only allowed in a signature. The TYPE-LEVEL library therefor has *term*-level aliases for all its *types*; for example, the term-level representation of the type **D2** is *d2*, whose actual *value* is  $\bot$ .

The symbol  $\bot$  is pronounced 'bottom', and refers to a computation which never terminates. It is a 'value' with no information: as such, it can be of any type. All the other theoretical aspects of the  $\bot$  element are beyond the scope of this thesis. We use it here, and in other examples, when we need to specify a term of which we do not know the value, but also where the value is of no use

<sup>&</sup>lt;sup>2</sup>Both Multi-Parameter Type Classes and Functional Dependencies are explained in Appendix D.

$<sup>^3</sup>$ As apposed to a Binary (**B**), Hexadecimal (**H**) or Octal (**O**) representation that are also present in Type-Level.

to us. In this case, we only care about the type information, so there is no need for knowing the actual value.

Having covered the context of the datatype declaration, let us go on with explaining the type declaration, the part between the  $\Rightarrow$  symbol and the = symbol: The name of the type is **FSVec** and it has two type variables, s and a, which represent the size and the element type respectively.

Then follows the constructor part of the datatype declaration, the part after the = symbol. Actually, we declare both the constructor and de-constructor at the same time. We call them constructors and de-constructors here, but they are actually renaming constructs: As said earlier, a **newtype** declaration is datatype renaming. So what this means is that the 'constructor', *FSVec*, retypes its argument, which had type [a], to be of type **FSVec s a**. That is why the size argument, *s*, is not part of the 'constructor' (even though you might think it should be): The *FSVec* 'constructor' is *just* a *retyping* construct. The curly braces following the *FSVec* constructor, { ... }, are not meant to be read as the Haskell record syntax, but as the syntactic sugar to introduce the de-constructor, *unFSVec*. This 'de-constructor' *retypes* from type **FSVec s a** to type [a]. Again, a more detailed explanations about *newtype* declarations in general can be found in Appendix D.

# Safe and Unsafe Constructors

We call the constructor of **FSVec** introduced by the *newtype* declaration *unsafe*, as it can not give any static guarantees about the list that is given as the argument for constructing the **FSVec** vector. This means that the type checker can not guarantee that the actual number of elements inside the vector, is the same as is indicated by its type. For example, the following code is allowed by any Haskell compiler:

```

v :: FSVec \ D2 \ Int

v = FSVec \ [1, 2, 3]

```

So there is now a mismatch between the number of elements in the vector (what we call the *dynamic* length), and the length indicated by the type (what we call the *static* length). For this reason, the constructor exposed by the *newtype* declaration is explicitly hidden by the designers of the FSVEC library, so that users can not create invalid vectors by accident. With the original constructor hidden, the FSVEC library exposes several other ways to construct a fixed size vector. This way, a user has to explicitly choose either a *safe* (we call it *safe* when the user of a library can *only* create vectors that have a matching *dynamic* and *static* length) or *unsafe* constructor.

We can, for example, unsafely build a vector from a list using *unsafeVector*, which has two arguments: A type-level numeral indicating the static size of the list, and a list containing the elements. It is unsafe because, like the original constructor of *FSVec*, the static size of the vector and dynamic size of the list can differ. However, the function *unsafeVector* does, at runtime, check for mismatches between the *dynamic* and the *static* length of the vector and reports an error if this happens to be the case (something the original *FSVec* constructor could not do):

# GHCi> unsafeVector d2 [1,2,3]

\*\*\* Exception: Data.Param.FSVec.unsafeVector: dynamic/static length mismatch

As we mentioned earlier, the designers of the FSVEC library also implemented *safe* constructors. An example of such a *safe* vector constructor is the Template Haskell function *vectorTH*, which has the following signature:

$$vectorTH :: Lift \ a \Rightarrow [a] \rightarrow ExpQ$$

It takes a *list* as its argument, and turns it into an AST that represents the Haskell code for the fixed-size vector. Some explanation about Template Haskell is certainly in order here, as it should give some insight as to how the *vectorTH* function works, and why it is considered *safe*.

3.2. Fixed-Size Vectors

Template Haskell provides the ability for a Haskell program to perform computations at compile time, which generates new code that can then be spliced into the program. Splicing is the act of inserting a generated AST in the AST of the original program. Template Haskell defines a standard algebraic data type for representing the abstract syntax of Haskell programs, and a set of monadic operations for constructing programs. These are all expressible in pure Haskell. Two additional syntactic constructs are introduced:

- A quotation construct, [...], that gives the AST representation of the fragment of code within the brackets.

- A splicing construct, \$(...), that takes a code representation tree (AST) and effectively inserts it into a program.

In Template Haskell, all aspects of Haskell which the ordinary programmer can use are also available to process the AST at program generation time. Thus a function that works on these ASTs, e.g. *vectorTH*, is just an ordinary Haskell function definition.

When we look at the signature of the *vectorTH* function we see that the result is of type **ExpQ** (an alias for **Q Exp**), which indicates that it is a (monadic) function which returns the AST for a piece of Haskell code. The elements of the list argument have to be of the **Lift** class, so that the *vectorTH* function can get the AST representation of the elements.

The reason that this *vectorTH* function can safely construct a vector from a list, is that we can just ask for the length of the list at compile-time and generate the corresponding vector type. We could not do this with the *FSVec* constructor, as we needed to specify the exact vector type (and thus its length) up front. The resulting AST of the *vectorTH* function is of no use to us, we want the actual vector. So, using the \$(...) syntax, we can splice the generated AST of the vector into a program, and resume compilation. When we ask for the type of the spliced *vectorTH* function, we see that the vector has a *generated* static length that corresponds with the number of elements in the list, meaning that the vector was constructed *safely*:

How type-level vector sizes help a hardware designer

Using one of the *safe* constructors, we will examine an example function and show how the type checker can help us ensure that the vector length we want is the vector length we get. Code Snippet 3.1 shows a function *foo* that, according to its type signature, only accepts vectors of size two, and always outputs a vector of size four. The body of the function however does not do what the signature promises<sup>4</sup>.

Code Snippet 3.1 (Vector concatenation - Incorrect).

```

foo :: FSVec D2 Int \rightarrow FSVec D4 Int

foo x = \text{out}

where

y = copy \ d3 \ 0

\text{out} = x + y

```

Looking at the body of the function we see a new function,  $copy \ n \ a$ , which creates a vector containing n copies of element a (the Integer 0 in the example), where n is a type-level numeral. The function + is the vector concatenation function equivalent to the one for lists. The above code does not compile (type-check), because the body of the function does something different than expected. The compiler reports the error shown on the next page:

<sup>&</sup>lt;sup>4</sup>Or, as seen from the other side of the fence: The signature lies about what the body does.

```

Couldn't match expected type 'D4' against inferred type 'D3' ...

```

arising from a use of '++' at foo.hs:16:10-15

The reported error is slightly confusing, especially given that it rises from the use of ++. It requires an in-depth knowledge of the type-level numerals of the TYPE-LEVEL library to understand why the error was reported as it was above, and is beyond the scope of this thesis. Nonetheless, the compiler informs us that it can not match the length of two vectors. The reason being of course that concatenating the vector x (size 2) to the vector y (size 3) results in a vector of size 5. However, the type signature of *foo* promised that the output would be a vector of size 4. Depending on what we want, we can either change the body, or, change the type signature of the function, to fix the error.

# Problems with FSVec

Having a potential fixed-size vector library for  $C\lambda$ asH in the form of the FSVEC library, one would think we could start focussing on the translation of the vectors and vector functions to VHDL. Instead, due to certain problems with the TYPE-LEVEL library that FSVEC uses, we are forced to search for a new type-level numerals library first. Below we see one of many examples where the TYPE-LEVEL library makes it impossible for us to describe an (intuitive) type signature for a function.

Code Snippet 3.2 shows a simple rotation function, with its intuitively correct (but sadly incomplete!) type signature.

CODE SNIPPET 3.2 (Rotate in FSVec).

```

rotate :: Pos \ s \Rightarrow FSVec \ s \ a \rightarrow FSVec \ s \ arotate \ vect = (last \ vect) +> (init \ vect)

```

Some explanation for the code snippet is in order: The context of the signature,  $Pos\ s$ , tells us that the size, s, of the vector should be non-zero; it has to be provided because the *last* and *init* function are only defined for non-empty vectors. The function signature,  $FSVec\ s\ a \rightarrow FSVec\ s\ a$ , then tells us that the vector length should stay the same. The operator +>, is equivalent to the *cons* (:) operator for lists. When we try to compile the *rotate* function we get the following error:

```

Could not deduce (Data.TypeLevel.Num.Ops.IsZero s yz, DivMod10 s yi yl) from the context (Pos s) arising from a use of 'init' at rotate.hs:25:30-38

Possible fix: add (Data.TypeLevel.Num.Ops.IsZero s yz, DivMod10 s yi yl) to the context of the type signature for 'rotate'

```

The above error apparently rises from the use of *init*:

```

init :: (Pos \ s, Succ \ s' \ s) \Rightarrow FSVec \ s \ a \rightarrow FSVec \ s' \ a

```

The *Pos s* part of the context should be familiar to us now, the *Succ s' s* specifies that *s* is the successor of *s'*: Meaning that the *init* function returns a vector that is one size smaller than the vector it was given as its arguments. Still this gives us no clue as to why the dependencies on the **IsZero** and **DivMod10** class are suddenly exposed in the error message. Most likely they are part of some of the induction rules related to **Succ**.

As IsZero and DivMod10 are part of the internal induction rules they are hidden by the TYPE-LEVEL library (meaning that they can only be used by functions inside the TYPE-LEVEL library),

3.2. Fixed-Size Vectors

making it impossible to implement the suggestion given by the error message. The problem lies with the TYPE-LEVEL library, not the FSVEC library itself: Meaning that we only need to find a replacement for the type-level numerals and keep most of the functionality of the FSVEC library to be used as the vector library for  $C\lambda$ asH.

As the TYPE-LEVEL library is not the only existing type-level numerals library in existence, we do not have to write our own numerals library just yet. Another type-level numerals library, called TFP [12], has similar signatures as the TYPE-LEVEL library, but uses *Type Families* instead of *Multi-Parameter Type Classes* and *Functional Dependencies* to describe the relations between numerals and the operations on them. In the next subsection, we will see that a fixed-size vector library using the numerals from the TFP library allow us to write a larger number of functions when compared to the FSVEC library.

#### 3.2.2 VECTOR LIBRARY WITH TYPE FAMILY BASED NUMERALS: TFVEC

Due to the problems with the numerals of the TYPE-LEVEL library described in the previous subsection we have completely re-written the original FSVEC library to make use of the type-level numerals and operations from the TFP library. We call this new library TFVEC: *Type Family Vector* library, as it uses type-level numerals based on *Type Families*.

In Code Snippet 3.3 we can see a new description of the *rotate* function that we tried to describe earlier using the FSVEC library. Although the type context is certainly larger than that of the *rotate* function found Code Snippet 3.2, it compiles, and also behaves correctly.

CODE SNIPPET 3.3 (Rotate with TFVec).

```

rotate :: (PositiveT pT, NaturalT nT, nT~Pred pT, pT~Succ nT) \Rightarrow

TFVec pT a \rightarrow TFVec pT a

rotate vect = (last vect) +>(init vect)

```

Let us examine the new syntax first: The  $\sim$  operator in the context of the type signature. This operator,  $\sim$ , is the *type equality coercion* operator, and was introduced together with the *type families* extension to Haskell [41]. The  $\sim$  operator asks the type-checker to enforce that the type on the left-hand side of the operator is 'equal' to the type on the right-hand side. We put 'equal' between quotes to indicate that the types are not intentionally *equal*, rather that, if the types were to be erased the program would not 'go wrong'.

The context of the above type signature is larger than expected, let us examine it in greater detail:

- *PositiveT pT*: The variable *pT*, the size of the vector, is a positive number; this context must hold because the functions *last* and *init* are only defined for vectors whose size is larger than zero

- NaturalT nT, nT $\sim$ Pred pT, pT $\sim$ Succ nT: Specifies that the successor of the predecessor of the variable pT is again pT. Currently, there seems to be no way in GHC to specify this relation at a higher level<sup>5</sup>. This rule is needed because GHC infers that the type of the body of the function is: TFVec pT  $a \rightarrow$  TFVec (Succ (Pred pT)) a. Without the context, the type checker can not reduce (Succ (Pred pT)) to pT, and as such not determine that the type of the body is equal to the function signature.

As we will see later on, many more arithmetic relations, some of which most people take for granted (such as the commutativity of addition (+)), have to be *explicitly* specified by a developer! They can not be *implicitly* deduced by a compiler (like GHC)! The 'technical' reason why GHC will not

<sup>&</sup>lt;sup>5</sup>There is however research on specifying invariants at the type-level [36]

reduce the above arithmetic relation will be discussed below. The 'theoretical' reason why GHC can not automatically deduce arithmetic relations will be discussed in a later subsection.

Now, the technical reason why GHC would not automatically reduce  $Succ\ (Pred\ pT)$  to pT is that the type-checker has not been given the 'rules' to execute this reduction. In the  $Type\ Family$  system,  $Succ\ a$  is defined as a relation for  $all\ types\ a$ . We need to define so-called  $Type\ Instances$  for each  $Succ\ a$  when applied to that type. For example, the  $Type\ Instance$  for  $Succ\ a$  on the D1 type could be specified as follows:

```

type instance Succ\ D1 = D2

```

This means, that the type checker now knows that it can reduce the instance of *Succ D1* to *D2*. In the TFP library, **D1**, **D2**, etc. are actually convenient type *aliases* for more 'complicated' underlying types. So in the TFP library, the *Type Instances* for those relations, such as **Succ**, are actually specified on the 'complicated' underlying types. However, the type instances for those relations work on the type *aliases* as well, as type *aliases* are transparent for the type-checker. In effect, the type-checker can reduce *every* instance of the *Succ* relation for *every defined*<sup>6</sup> decimal *a* to the corresponding successive decimal *b*. This also applies to all the other type-level relations and operations: All *specific* decimal instances can be reduced to a normalized form. But, we can not reduce the *general* case of the relations and operations, as we can not specify any rule (*Type Instance*) for this. That is the reason why we had to supply the type equality coercion in the context of the new *rotate* function, so that the type-checker now knows that the 'rule': the successor of the predecessor of *a* is again *a*, applies to the *general* case in that specific function.

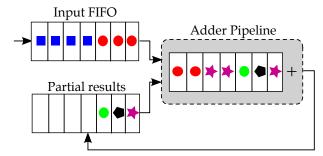

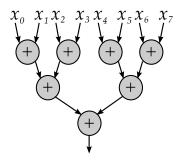

When we look at the context of the *rotate* function it is certainly not as concise as we hoped for. But, it is at least *possible* to specify a context that is satisfactory for the type-checker. Hopefully we can lift the context  $(Succ\ (Pred\ pT)) \sim pT$  to a higher level, like maybe a type class or type-level invariant, in a future release of GHC<sup>7</sup>.